Can the CHIPS Act bolster Moore's Law?

Congress continues to wrangle over the CHIPS for America Act, which would provide $52 billion in subsidies for the domestic production of semiconductors. The bill, seen as a way to reduce America’s reliance on Taiwan, which manufactures an overwhelming portion of the world’s leading-edge chips, is widely popular. As the New York Times reports, however, “it has languished for nearly a year after lawmakers chose to package it with sprawling legislation aimed at bolstering US competitiveness with China, which has stalled amid a variety of policy disputes.”

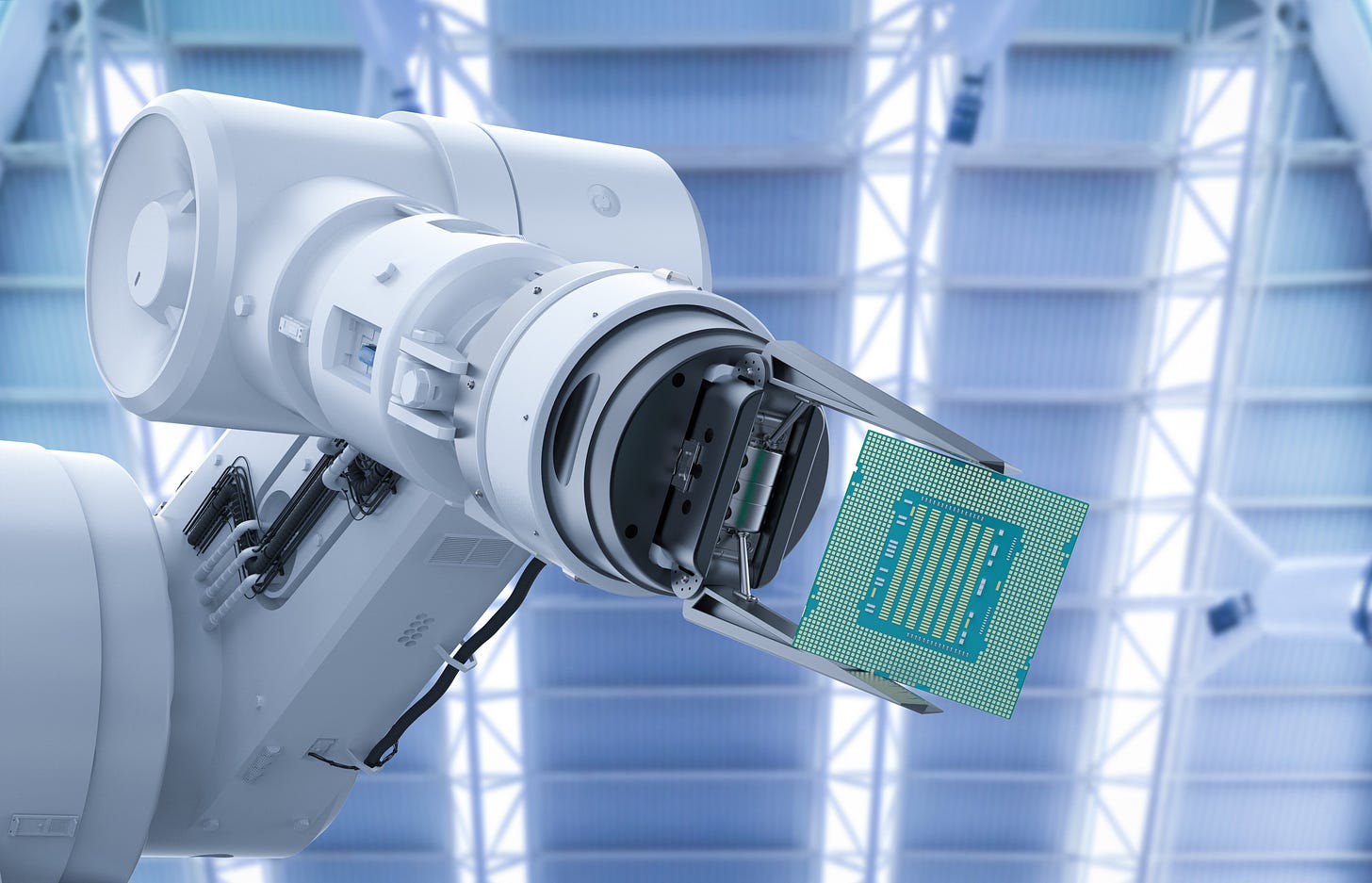

Despite my own skepticism of industrial policy, I concluded over the past few years that reducing our geographic concentration risk is imperative and that reigniting the US chip industry could yield larger strategic and economic benefits. It’s worth asking, however: If the US government decides to fund American-made microchips, will taxpayers get their money’s worth? After all, isn’t the exponential advance of microelectronics known as Moore’s Law dead, or at least slowing?

The bottom line is that yes, the compound doubling rate of Moore’s Law every two years is getting much more difficult and expensive. The primary historical method of achieving cost-performance gains—shrinking transistors—won’t work forever and has nearly reached its fundamental atomic limits.

There is surprisingly good news on the technical front, however. At least two broad sets of additional innovations may allow us to sustain a close-to-Moore’s Law pace for at least another decade.

In two recent presentations, Applied Materials, a large producer of chip-making machines, outlined its strategy, which is broadly shared by Intel, Samsung, TSMC, and other large chip manufacturers. First, continue shrinking and reshaping transistors using the next generation of extreme ultraviolet (EUV) lithography. Arranging billions of invisible digital switches on a tiny sliver of polished sand (silicon) requires many hundreds of steps. They build elaborate 3-D patterns of transistors, gates, and wires by shining super-high frequency light through masks, creating maps of unimaginable precision to deposit materials onto the chip and etch materials away from it. It’s even harder than it sounds, and it only gets us part way to remaining on the Moore’s Law path.

Second, rethink the ways that chips are wired, packaged, and linked together. This is reengineering the macro-architecture of the chip. Getting information (signals) and electrons (power) onto and off of the chip is difficult. As chip complexity rises, wires end up occupying more and more of the space. The new idea is to connect the power source to the back side of the chip. By using the front side for signaling and the back side for power, they can exploit double the area and free up valuable chip real estate for more transistors.

Stacking chips vertically will also better exploit the third dimension. It will dramatically improve memory bandwidth, for example, by keeping more data as close to the logic cells as possible without consuming so much primary chip real estate. 3-D stacking will allow for a number of specialized chips—logic, memory, graphics, etc.—to be packaged together as if they were on the same die.

Over the last decade, the key strategy for overcoming the growing challenges of transistor shrinkage and clock-cycle leveling was parallel processing using multiple cores. Hyper-parallelism will continue at even larger scales, as in giant wafer-scale chips and via the ultimate macro-scale of the cloud.

The difficulty and expense of chasing Moore’s Law leads some to conclude we are seeing a significant slowdown, not just of economic productivity, but of scientific productivity. While it’s true that we are investing far more to sustain Moore’s magical doubling rate, it’s also true that the products delivered from modern silicon fabrication plants power a far broader and deeper array of technologies and industries than ever before—and that potential productivity gains in these giant economic sectors will justify the large outlays.

This article originally appeared at AEIdeas.